# **Application Note**

# **Document No.: AN1128**

# G32R501 Dual-core Emulation Guide

Version: V1.1

© Geehy Semiconductor Co., Ltd.

## 1 Introduction

The G32R5xx dual-core microcontroller (MCU) series is described in Table 1. The applicable product described in this document (referred to as G32R5xx MCU in this document) is based on the high-performance Arm<sup>®</sup> Cortex<sup>®</sup>-M52 32-bit RISC core. To fully utilize the dual-core architecture, the G32R501 series MCU requires specific development methods.

This debugging manual provides a guide for debugging custom applications on the G32R501 MCU, and it covers the following aspects:

- Basic principle of debugging G32R5xx dual-core MCU.

- How to use EWARM and MDK-ARM tool chains that support Geehy-Link debugging to debug dual-core devices.

For more information on the G32R501 MCU, please refer to the following documents:

- G32R501 Series Datasheet

- G32R501 Series User Manual

#### Table 1 G32R5xx Dual-core Models

| General series | Specific supported product model        |

|----------------|-----------------------------------------|

| G32R5xx        | G32R501DxCx7/G32R501DxYx7/G32R501DxYx8Q |

# Contents

| 1   | Introduction                                                   | 1    |

|-----|----------------------------------------------------------------|------|

| 2   | Basic Mechanism of Dual Cores                                  | 3    |

| 2.1 | Functional Characteristics                                     | 3    |

| 2.2 | Debug Access Port (DAP)                                        | 3    |

| 3   | Debugging Support                                              | 5    |

| 4   | MDK-ARM Dual-core Debugging Support                            | 6    |

| 4.1 | Dual-core Debugging on MDK-ARM                                 | 6    |

| 4.2 | Steps for Dual-core Debugging Using GEEHY-LINK (WinUSB)        | 6    |

| 5   | IAR EW for Arm Dual-core Debugging Support                     | .12  |

| 5.1 | Dual-core Debugging on IAR EW for Arm                          | . 12 |

| 5.2 | Steps for Dual-core Debugging Using GEEHY-LINK (WinUSB)        | . 12 |

| 6   | Eclipse Dual-Core Debugging Support                            | .18  |

| 6.1 | Dual-Core Debugging on Eclipse                                 | . 18 |

| 6.2 | Instructions for Dual-Core Debugging Using GEEHY-LINK (WinUSB) | . 18 |

| 7   | Revision                                                       | .24  |

## 2 Basic Mechanism of Dual Cores

A multi-core processor is composed of heterogeneous core (meaning different cores) or isomorphic (same) core.

The dual cores in G32R5xx are of an asymmetric architecture. By default, CPU0 is set to master and can work normally, while CPU1 is set to slave. When the chip starts, CPU1 is set to hold and its clock is disabled. To make the slave work, CPU0 needs to enable its clock through registers and to set its boot address.

### 2.1 **Functional Characteristics**

The G32R501 series MCU can provide comprehensive and flexible debugging and performance analysis support.

- Independent breakpoint debugging: Supports independent breakpoint debugging for each CPU core in the system, facilitating fine debugging of the multi-core system.

- **Code execution tracking:** Supports tracking of the code execution process, which is helpful for performance analysis and debugging.

- **JTAG debug port:** Provides a standard JTAG debugging interface, compatible with a wide range of debugging tools.

- **Serial wire debug port:** Supports Serial Wire Debug Port, to simplify debugging connection.

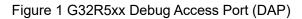

### 2.2 **Debug Access Port (DAP)**

The G32R501 MCU includes four access ports (AP) connected to the debug port (DP):

- AHB-AP0: CPU0 access port (AHB-AP) provides access to the integrated debugging and tracing functions in the CPU0 core through the AHB-Lite bus connected to the AHBD port of the processor.

- AHB-AP1: CPU1 access port (AHB-AP) provides access to the integrated debugging and tracing functions in the CPU1 core through the AHB-Lite bus connected to the AHBD port of the processor.

- AHB-AP2: Bus matrix access port. Allow access to the system bus matrix.

- APB-AP3: Debug access port. Allow access to external debugging components.

# 3 Debugging Support

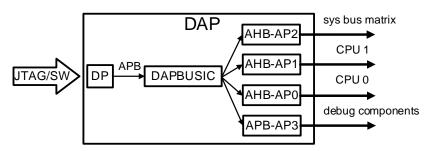

The dual-core debugging allows the use of a single hardware debugging probe to debug two cores simultaneously. The debugging information of two cores can be displayed in a single integrated development environment (IDE) graphical user interface (GUI), or an IDE GUI instance can be created for each core separately. The performance of the separated IDE GUI instance is shown in Figure 2.

Figure 2 Dual-core debugging IDE Diagram

To ensure smooth dual-core debugging, the debugger used must provide the following functions:

- An optional access port.

- The ability to connect multiple cores simultaneously using the same debugging probe.

- Visibility of all cores.

- Support cross triggering Arm<sup>®</sup> components.

- The possibility of switching access ports between different domains within the same debugging session to visualize the status of memory and peripheral devices.

# 4 MDK-ARM Dual-core Debugging Support

The latest version of MDK-ARM can be downloaded from its official website.

### 4.1 Dual-core Debugging on MDK-ARM

As described earlier, the dual-core asymmetric system in G32R5xx requires specific development tools, and the MDK-ARM IDE v5.40 and above support dual-core debugging of G32R5xx.

### 4.2 Steps for Dual-core Debugging Using GEEHY-LINK (WinUSB)

This section provides step-by-step instructions for using MDK-ARM v5.40 and GEEHY-LINK (WinUSB) debugging probes together with G32R5xx MCU.

Note:

The dual-core debugging of Arm<sup>®</sup> Cortex<sup>®</sup>-M52 is supported in MDK-ARM v5.40 and higher versions.

Before performing the following operations, please install the G32R5xx chip support (**Geehy.G32R5xx\_DFP.x.x.x.pack**).

In this example, a project needs to be created for each core.

(For the example program, refer to G32R5xx\_SDK\driverlib\g32r501\examples\eval\ipc\)

- 1. Create a new project, and configure debugging settings for CPU0 project:

- a) Open MDK-ARM and create a new project.

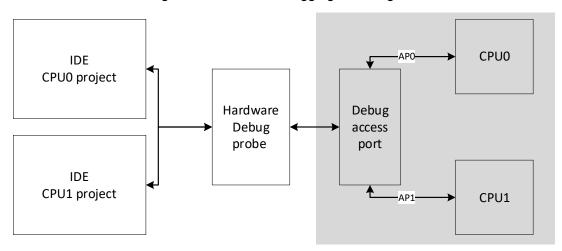

- b) Select the correct device, Project → Options for Target → Device, choose the G32R501(Figure 3) of dual-core series, and select the model with the word "CPU0" at the end.

Figure 3 G32R501 MDK Chip Selection (partial)

c) Configure the .sct file and select the dual-core configuration.

#### Figure 4 Use Dual-core Configuration

- g32r501dxc\_cpu0\_cbus\_flash.sct

g32r501dxc\_cpu0\_itcm\_flash.sct

g32r501dxc\_cpu1\_cbus\_flash.sct

g32r501dxc\_cpu1\_itcm\_flash.sct

g32r501dxy\_cpu0\_cbus\_flash.sct

g32r501dxy\_cpu0\_itcm\_flash.sct

g32r501dxy\_cpu1\_cbus\_flash.sct

g32r501dxy\_cpu1\_itcm\_flash.sct

g32r501dxy\_cpu1\_itcm\_flash.sct

g32r501dxy\_cpu1\_itcm\_flash.sct

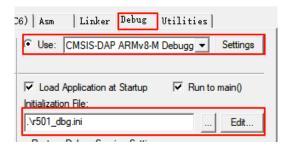

- d) Configure the debugger and debugging script: Project  $\rightarrow$  Options for Target  $\rightarrow$  Debug

- i. Select the debugger as "CMSIS-DAP ARMv8-M Debugger".

- ii. Select the debugging script as "r501\_deg.ini"

Figure 5 Configure Debugger and Debugging Script

e) Configure the debugger as GEEHY-LINK.

Figure 6 Select the Debugger as GEEHY-LINK

| CMSIS-DAP ARMv8-M Target Driv | ver Setup |                    |                     |      |

|-------------------------------|-----------|--------------------|---------------------|------|

| Debug Trace Flash Download    | Pack      |                    |                     |      |

| CMSIS-DAP - JTAG/SW Adapter   | SW De     | vice               |                     |      |

| Geehy CMSIS-DAP WinUSB 👻      |           | IDCODE             | Device Name         | Move |

| Serial No: 003500415000001    | SWDIO     | ⊙ 0x6BA02477       | ARM CoreSight SW-DP | Up   |

| Firmware Version: 2.1.0       |           |                    |                     | Down |

| 🗹 SWJ Port: SW 👻              |           | tomatic Detection  | ID CODE:            |      |

| Max Clock: 5MHz 👻             | С Ма      | nual Configuration | Device Name:        |      |

f) Configure the program download method.

#### Figure 7 CPU0 Program Download Configuration

| CMSIS-DAP ARMv8-M Target Debug Trace Flash Downloa                                      |                                                                        |     |                      |                                          | × |

|-----------------------------------------------------------------------------------------|------------------------------------------------------------------------|-----|----------------------|------------------------------------------|---|

| Download Function     Orab     C Erase Full Chip     C Erase Sectors     C Do not Erase | <ul> <li>✓ Program</li> <li>✓ Verify</li> <li>☐ Reset and F</li> </ul> | Run | RAM for /            | Algorithm<br>0x20000000 Size: 0x00004000 |   |

| Programming Algorithm                                                                   |                                                                        |     |                      |                                          |   |

| G32R5xx Program Algorithm                                                               | Device Size<br>527392k                                                 |     | ce Type<br>nip Flash | Address Range 00000000H - 20307FFFH      |   |

- 2. Create a new project, and configure debugging settings for CPU1 project:

- a) Open MDK-ARM and create a new project.

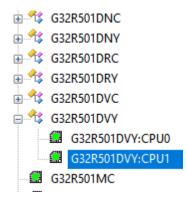

- b) Select the correct device, Project → Options for Target → Device, choose the G32R501(Figure 8) of dual-core series, and select the model with the word "CPU1" at the end.

#### Figure 8 CPU1 Project Selection

c) Configure the .sct file and select the CPU1 configuration.

| Options for Target 'g32r501'                                                                                                                                                                                                                                                                                              | X 32r501dxy_cpu0_cbus_flash.sct                                                                                                                     |                                                      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| Device   Target   Output   Listing   User   C/C++ (AC6)   Asm Linker   Debug   Utilities                                                                                                                                                                                                                                  | Expand All Collapse All Help Show Grid                                                                                                              |                                                      |

| □ Use Memory Layout from Target Dialog       X/O Base:         □ Make RW Sections Position Independent       R/O Base:         □ Make RO Sections Position Independent       R/O Base:         □ Dont Search Standard Libraries       0x20000000         ☑ Report might fail Conditions as Errors       disable Warnings: | Option  SRAM Configuration  Enable SRAM1  Enable SRAM2  Stack / Heap Configuration  Stack Size (in Bytes)  Heap Size (in Dytes)  Stack Top Location | Value Value V 0x0000 1000 0x0000 1000 DTCM (Default) |

| Scatter Ng32501dxy_cpu0_cbus_flash.sct I Edt                                                                                                                                                                                                                                                                              | Code Execution Region Configuration Code Execution Region Configuration Code Execution Region Custom Address Configuration                          | Flash (Default)                                      |

#### Figure 9 CPU1 .sct File Configuration

- d) Please refer to the previous chapter for debugger configuration.

- e) The configuration program does not require downloading.

#### Figure 10 CPU1 Program Download Configuration

| CMSIS-DAP ARMv8-M Target    | Driver Setup                       |     |            |                         |                  |

|-----------------------------|------------------------------------|-----|------------|-------------------------|------------------|

| Debug   Trace Flash Downloa | d Pack                             |     |            |                         |                  |

| Download Function           | Program     Verify     Reset and F | Run | RAM for A  | Algorithm<br>Dx20000000 | Size: 0x00004000 |

| Programming Algorithm       |                                    |     |            |                         |                  |

| Description                 | Device Size                        |     | vice Type  |                         | ss Range         |

| G32R5xx Program Algorithm   | 527392k                            | On- | chip Flash | 0000000H                | 1 - 20307FFFH    |

3. Download CPU1 program files using CPU0 project.

Since the Flash operations in the downloading process are completed by CPU0, the CPU0 project needs to download the binary files of the programs that CPU1 needs to run through the CPU0 project during compilation.

a) Configure CPU1 project to generate bin files, select Project  $\rightarrow$  Options for Target  $\rightarrow$  User  $\rightarrow$  After Build/Rebuild, and configure the command for generating bin files.

The example uses:

fromelf.exe --output "..\..\cpu0\project\MDK\cpu1\_image.bin" --bincombined "#L"

When using commands, pay attention to the path of the project.

Figure 11 Project→Options for Target→User→After Build/Rebuild

| evice   Target   Uutput   Listii | ng User C/C++ (AC6)   Asm   Linker   De | bug   V | tilities      |     |

|----------------------------------|-----------------------------------------|---------|---------------|-----|

| Command Items                    | User Command                            |         | Stop on Exi   | S   |

| Before Compile C/C++ File        |                                         |         |               |     |

| Run #1                           |                                         | 2       | Not Specified |     |

| Run #2                           |                                         | 2       | Not Specified |     |

| Before Build/Rebuild             |                                         |         |               |     |

|                                  |                                         | 2       | Not Specified |     |

| 🗌 Run #2                         |                                         | 2       | Not Specified |     |

| Aft <u>er Build/Rebuild</u>      |                                         |         | -             |     |

| Run #1                           | fromelf.exeoutput "\\\cpu0\project\MDK  |         | 12.0.12       | 1.2 |

b) Call the bin file of the corresponding CPU1 in the CPU0 project. The example program is as follows:

```

__attribute__((__used__, section("cpu1_code")))

void G32R501_incbin(void)

{

__asm(".incbin \"cpu1_image.bin\"");

}

```

- c) If a custom .sct file is used, the user needs to specify the cpu1\_code segment in the .sct file, and the definition of this segment needs to be consistent with the program space where CPU1 runs.

- Regarding the example .sct file. The examples .sct used in this chapter are g32r501dxy\_cpu0\_cbus\_flash.sct and g32r501dxy\_cpu1\_cbus\_flash.sct in DK\device\_support\g32r501\common\sct\.

- a) In g32r501dxy\_cpu0\_cbus\_flash.sct, after dual-core configuration is selected, the G32R5xx Flash will be divided into two. The location of the cpu1\_code segment will be declared.

Figure 12 CPU1 Program Running Segment Settings of .sct in CPU0

| 240 |                                                          |

|-----|----------------------------------------------------------|

| 247 | #if · CORE CONFIG·==·1                                   |

|     |                                                          |

| 248 | LR_ROM_CPU1·RO_BASE+ <mark>RO_SIZE/2·_RO_SIZE/2</mark> { |

| 249 | ER_ROM_CPU1RO_BASE +RO_SIZE / 2RO_SIZE / 2               |

| 250 | ·····.ANY·(cpu1_code)                                    |

| 251 | · · }                                                    |

| 252 | }                                                        |

| 253 | #endif                                                   |

|     |                                                          |

The allocation of Flash for dual-core configuration is as follows:

| Table 2 CPU0/1 | <b>Running Space</b> | Settings |

|----------------|----------------------|----------|

|----------------|----------------------|----------|

| Start address of flash | Size     | Core used |

|------------------------|----------|-----------|

| 0x0800000              | 0x050000 | CPU0      |

| 0x08050000             | 0x050000 | CPU1      |

b) In g32r501dxy\_cpu1\_cbus\_flash.sc, the use configuration of Flash corresponds to the dual-core setting of r501\_cpu0\_flash\_link.sct.

Figure 13 .sct Program Running Segment Settings of CPU1

| 174 | LR_ROM RO_BASE+ RO_SIZE/2 RO_SIZE/2 { · · · · · |

|-----|-------------------------------------------------|

| 175 | ER_ROMRO_BASE+RO_SIZE/2RO_SIZE/2 { · · · ·      |

| 176 | ···*.o (RESET, +First)                          |

| 177 | ····*(InRoot\$\$Sections)                       |

| 178 | $\cdots$ ANY $(+R0)$                            |

| 179 | $\cdots$ ANY $(+XO)$                            |

| 180 | ···}                                            |

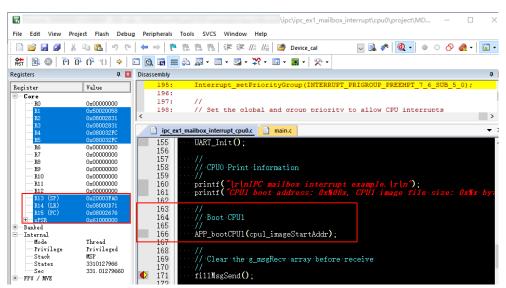

5. Start dual-core debugging

After completing normal debugger configuration and program compilation correctly, dualcore debugging configuration can be started.

a) Start CPU0 project debugging, and set the breakpoints after setting the statement of setting CPU1 boot.

Figure 14 CPU0 Boot Debugging and CPU1 Boot

b) Start CPU1 project debugging.

#### Figure 15 CPU1 Boot Debugging

c) The final effect is shown in Figure 16.

#### Figure 16 CPU0/1 Debugging Interface

# 5 IAR EW for Arm Dual-core Debugging Support

The latest version of IAR EW for Arm can be downloaded from the official website of IAR.

### 5.1 **Dual-core Debugging on IAR EW for Arm**

As described earlier, the dual-core asymmetric system in G32R5xx requires specific development tools, and the IAR EW for Arm 9.60.2 and above support dual-core debugging of G32R5xx.

### 5.2 Steps for Dual-core Debugging Using GEEHY-LINK (WinUSB)

This section provides step-by-step instructions for using IAR EW for Arm 9.60.2 and GEEHY-LINK (WinUSB) debugging probes together with G32R5xx MCU.

Note:

The dual-core debugging of Arm<sup>®</sup> Cortex<sup>®</sup>-M52 is supported in IAR EW for Arm 9.60.2 and higher versions.

Before performing the following operations, please install the G32R5xx chip support (G32R5xx\_AddOn\_v1.0.0.exe).

In this example, a project needs to be created for each core.

(For the example program, refer to G32R5xx\_SDK\driverlib\g32r501\examples\eval\ipc\)

The G32R5xx chip does not distinguish between CPU0/CPU1 in the IAR EW for Arm project. When creating a new CPU0/CPU1 project, you only need to select the dual-core chip.

- 1. Create a new project, and configure debugging settings for CPU0/CPU1 project:

- a) Open IAR EW for Arm and create a new project.

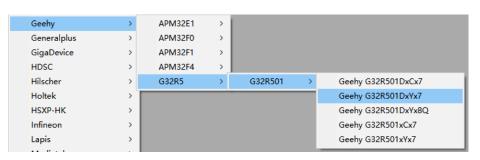

- b) Select the correct device, General Options→Target→Device, and select the G32R501 (Figure 17) of dual-core series.

#### Figure 17 G32R501 IAR Chip Selection (partial)

c) Configure the .icf file and select the dual-core configuration. Please select different .icf files for different CPU projects. For example, the configuration file for CPU0 is "g32r501dxy cpu0 cbus flash.icf".

| Assembler<br>Output Converter<br>Custom Build<br>Linker | Config<br>Linker | Library<br>configura | Input | Optimizations   | Advanced    | Output | List | g32r501dxc cpu0 itcm flash.icf                                                             |

|---------------------------------------------------------|------------------|----------------------|-------|-----------------|-------------|--------|------|--------------------------------------------------------------------------------------------|

|                                                         | Linker           | configura            |       |                 |             |        |      | g32r501dxc cpu1 cbus flash.icf                                                             |

|                                                         |                  | erride de            |       |                 |             |        |      | g32r501dxc_cpu1_itcm_flash.icf                                                             |

| Build Actions<br>Debugger<br>Simulator                  |                  |                      |       | 01dxy_cpu0_cbus | ;_flash.icf |        |      | <ul> <li>g32r501dxy_cpu0_cbus_flash.icf</li> <li>g32r501dxy_cpu0_itcm_flash.icf</li> </ul> |

| CADI<br>CMSIS DAP                                       |                  | Edit                 |       |                 |             |        |      | g32r501dxy_cpu1_cbus_flash.icf<br>g32r501dxy_cpu1_itcm flash.icf                           |

#### Figure 18 Use Dual-core Configuration

- d) Configure CPU0 project to include the CPU1 running image: Linker  $\rightarrow$  Input,

- i. Set to keep compiling without optimizing "ipc\_cpu1\_image".

- ii. Load the bin file path and related configuration.

#### Figure 19 Use Dual-core Configuration

| Options for node "proj | ject" |                                                    | ×           |

|------------------------|-------|----------------------------------------------------|-------------|

|                        |       |                                                    |             |

| Category:              | Г     | <b>5.11</b>                                        | ry Settings |

| General Options        |       | Facto                                              | ry settings |

| Static Analysis        |       |                                                    |             |

| Runtime Checking       |       |                                                    |             |

| C/C++ Compiler         |       | #define Diagnostics Checksum Encodings Extra       | Options     |

| Assembler              |       |                                                    | · ·         |

| Output Converter       |       | Config Library Input Optimizations Advanced Output | List        |

| Custom Build           |       |                                                    |             |

| Linker                 |       | Keep symbols: (one per line)                       |             |

| Build Actions          |       | ipc cpu1 image                                     | ~           |

| Debugger               |       |                                                    |             |

| Simulator              |       |                                                    |             |

| CADI                   |       |                                                    |             |

| CMSIS DAP              |       |                                                    |             |

| E2/E2 Lite             |       |                                                    |             |

| GDB Server             |       |                                                    |             |

| G+LINK                 |       |                                                    |             |

| I-jet                  |       |                                                    |             |

| J-Link/J-Trace         |       |                                                    |             |

| TI Stellaris           |       |                                                    |             |

| Nu-Link                |       |                                                    | $\sim$      |

| PE micro               |       | Raw binary image                                   |             |

| ST-LINK                |       |                                                    |             |

| Third-Party Driver     |       | File: Symbol: Section:                             | Align:      |

| TI MSP-FET             | 4     | \$PROJ_DIR\$\cpu1_image.binipc_cpu _cpu1_ir        | 4           |

|                        |       | File: Symbol: Section:                             | Align:      |

|                        |       | Symbol: Section:                                   | Angn.       |

|                        |       |                                                    |             |

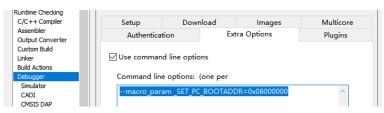

- e) Configure the simulator and boot address:

- i. Both CPU0 and CPU1 projects require it; select the debugger "CMSIS-DAP": Debugger→ Setup.

- ii. Configure boot address for CPU0 project: Debugger → Extra Options → check

"Use command line options" → enter in the text box:

"--macro\_param \_SET\_PC\_BOOTADDR=0x08000000". Note that the address here needs to correspond to the actual boot address of CPU0.

Figure 20 Configure Boot Address for CPU0 Project

f) Configure CPU0 project simulation AP port: CMSIS DAP→Interface→Probe config, select "From file"→ select "CM52 0" according to CPU.

Figure 21 Configure CPU0/CPU1 Project Simulation AP Port

| Options for node "p                                                      | roject |                                   |                                                                            | >                |

|--------------------------------------------------------------------------|--------|-----------------------------------|----------------------------------------------------------------------------|------------------|

| Category:<br>General Options                                             | •      |                                   |                                                                            | Factory Settings |

| Static Analysis<br>Runtime Checking<br>C/C++ Compiler                    |        | Setup Interface                   | Breakpoints                                                                |                  |

| Assembler<br>Output Converter<br>Custom Build<br>Linker<br>Build Actions |        | Probe config<br>Auto<br>From file | Probe configuration file<br>Override default<br>\$TOOLKIT_DIR\$/config/deb | bugger/Geehy/G   |

| Debugger<br>Simulator<br>CADI                                            |        | ⊖ Explicit                        | CPU: CM52_0                                                                | Select           |

| CMSIS DAP<br>E2/E2 Lite<br>GDB Server                                    |        | Interface<br>O JTAG               | Explicit probe configuration                                               | CM52_0<br>CM52_1 |

g) Configure CPU0 project to link CPU1 project. After the basic configuration of each project has been completed, CPU0 project can be used to link CPU1 project, so that the simulation of the two projects can be started simultaneously when starting the simulation.

Configuration process: Debugger $\rightarrow$ Multicore $\rightarrow$ Asymmetric multicore, check "Simple" $\rightarrow$ Select the file for CPU1 project at the Partner workspace $\rightarrow$ Fill in the CPU1 project name at the Partner project $\rightarrow$ Fill in the project tag that needs to be placed at the Partner.

The specific configuration is shown in the following figure.

Figure 22 Configure CPU0 project to link CPU1 project

| /C++ Compiler                                                                                             | Authentication Extra Options Plugir                  |                                 |                     |         |  |  |  |

|-----------------------------------------------------------------------------------------------------------|------------------------------------------------------|---------------------------------|---------------------|---------|--|--|--|

| ssembler                                                                                                  | Setup                                                | Setup Download Images Multicore |                     |         |  |  |  |

| utput Converter sustom Build<br>nker suid Actions<br>ebugger<br>Simulator<br>CADI CADIS DAP<br>E2/E2 Lite | Symmetric multice<br>Number of<br>Asymmetric multice | ore 1                           |                     |         |  |  |  |

| DB Server                                                                                                 | Simple                                               |                                 |                     |         |  |  |  |

| -jet<br>-Link/J-Trace                                                                                     | Partner works                                        | pace: olling\ <mark>cpu</mark>  | 1\project\IAR\proje | ect.eww |  |  |  |

| TI Stellaris<br>Nu-Link                                                                                   | Partner projec                                       | t: project                      |                     |         |  |  |  |

| Emicro                                                                                                    | Partner                                              | G32R501                         |                     |         |  |  |  |

| T-LINK<br>hird-Party Driver                                                                               | Attach part                                          | ner to running targ             | et Partner cores    | : 1     |  |  |  |

- 2. Additional settings for CPU1 project:

- a) Refer to the previous content to complete the correct chip selection, icf file settings, and simulation settings.

- b) Configure the output bin file to the specified directory (which needs to be consistent with the path of configuring CPU0 to include the CPU1 running image).

Figure 23 Configure the output bin file of CPU1 project to specified directory

| Runtime Checking<br>C/C++ Compiler<br>Assembler | Output                               |

|-------------------------------------------------|--------------------------------------|

| Output Converter<br>Custom Build                | Generate additional output           |

| Linker<br>Build Actions                         | Output format:                       |

| Debugger<br>Simulator                           | Raw binary ~                         |

| CADI<br>CMSIS DAP                               | Output file                          |

| E2/E2 Lite                                      | ☑ Override default                   |

| GDB Server<br>G+LINK                            | \\\\\cpu0\project\IAR\cpu1_image.bin |

| I-jet<br>14 ink/1-Trace                         |                                      |

- c) Configure CPU1 project simulation AP port: CMSIS DAP→Interface→Probe config, select "From file"→ select "CM52 1" according to CPU.

- d) The CPU1 project does not require additional configuration to not reset the MCU during simulation connection: CMSIS DAP → Setup → Disabled (no reset).

Figure 24 Not Resetting MCU When Configuring CPU1 Connection

| Luntime Checking<br>C/C++ Compiler | Setup Interface Breakpoints |   |

|------------------------------------|-----------------------------|---|

| Assembler                          |                             |   |

| Output Converter                   | Reset                       |   |

| Custom Build                       |                             |   |

| inker                              | System (default)            | ~ |

| Build Actions                      | Disabled (no reset)         |   |

| Debugger                           | Software                    |   |

| Simulator                          | Hardware                    |   |

| CADI                               | Core                        |   |

| CMSIS DAP                          | System (default)            |   |

- Regarding the example .icf file. The examples .sct used in this chapter are g32r501dxy\_cpu0\_cbus\_flash.icf and g32r501dxy\_cpu1\_cbus\_flash.icf in SDK\device\_support\g32r501\common\icf\.

- a) In g32r501dxy\_cpu0\_cbus\_flash.icf, after dual-core configuration is selected, the G32R5xx Flash will be divided into two. In addition, the location of the cpu1\_image segment will be declared.

Figure 25 CPU1 Program Running Segment Settings of .icf in CPU0

| g32r501dxy_cpu0_cbus_flash.icf ×                                                                                                                                                                              |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                                                                                                                                                                                               |  |

| <pre>// Required in a multi-threaded application initialize by copy with packing = none { sectionDLIB_PERTHREAD }; }</pre>                                                                                    |  |

| <pre>place at address mem:ICFEDIT_intvec_start { readonly section .intvec };</pre>                                                                                                                            |  |

| place in CBUS_FLASH_region { readonly };<br>place in CPU0_ITCM_RAM_region { section itcm.instruction, section itcm.ramfunc<br>place in CPU0 DTCM RAM region { section dtcm.data, section dtcm.bss, block CSTA |  |

| <pre>place in SRAM1 region { section sram1.share data }; place in SRAM2 region { section sram2.share data };</pre>                                                                                            |  |

| <pre>place in SRAM3_region { section sram3.share_data }; place in RAM_region { readwrite };</pre>                                                                                                             |  |

| <pre>place in CPU1_region { sectioncpu1_image };</pre>                                                                                                                                                        |  |

For the allocation of Flash for dual-core configuration, refer to Table 2 CPU0/1 Running Space Settings. Table 2 CPU0/1 Running Space Settings

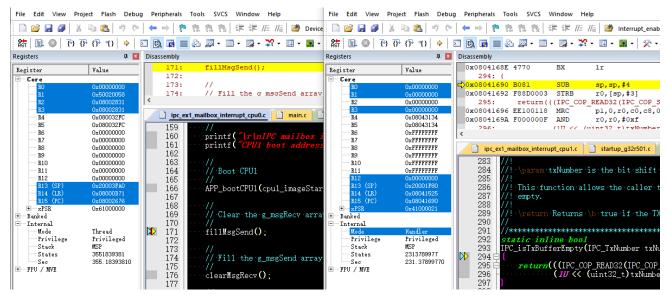

4. Start dual-core debugging

After completing normal debugger configuration and program compilation correctly, dualcore debugging configuration can be started.

- a) Starting CPU0 project debugging will directly start two CPU. After starting the debugging window, two debugging windows can be seen:

- i. At this point, set a breakpoint after starting the CPU1 program in the CPU0 project, and run the program to this breakpoint. At this point, the CPU1 project will be able to connect to CPU1 normally.

- ii. After the CPU1 project is connected normally, please press its project "Reset" button to return the CPU1 project to its start address.

- iii. Subsequently, dual-core simulation can be made as needed.

### Figure 26 IAR Dual-core Simulation Debugging Interface

| Image: Control of the second secon | <pre>pc.s2,mailine.publing.public x [ min.c ] example_mailing Board_init();  // fundies CPU (interrupts // fundies CPU (interrupts // fundies CPU (interrupts); // UMAT initialize UMAT_init(); // CPU Print (information // CPU Print (information // CPU Print (information // Boart CPUI // Boart CPUI</pre> | FO ALL Stack | Image: Contract of the program is distributed on an ALL Status global.         Image: Contract of the program is distributed on an ALL Status global.         Image: Contract of the program is distributed on an ALL Status global.         Image: Contract of the program is distributed on an ALL Status global.         Image: Contract of the program is distributed on an ALL Status global.         Image: Contract of the program is distributed on an ALL Status global.         Image: Contract of the program is distributed on an ALL Status global.         Image: Contract of the program is distributed on an ALL Status global.         Image: Contract of the program is distributed on an ALL Status global.         Image: Contract of the program is distributed on an ALL Status global.         Image: Contract of the program is distributed on an ALL Status global.         Image: Contract of the program is distributed on an ALL Status global.         Image: Contract of the program is distributed on an ALL Status global.         Image: Contract of the program is distributed on an ALL Status global.         Image: Contract of the program is distributed on an ALL Status global.         Image: Contract of the program is distributed on an ALL Status global.         Image: Contract on ALL Status global. | igged prog |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| project                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | // Clear the g.msplecy array before receive                                                                                                                                                                                                                                                                                                                 | +            | project                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |            |

### 6 Eclipse Dual-Core Debugging Support

The latest version of Eclipse can be downloaded from the official Eclipse website.

Note: The debugging method described in this chapter uses pyOCD+GEEHY-LINK for debugging.

### 6.1 **Dual-Core Debugging on Eclipse**

Follow the instructions in the "<u>AN1126\_G32R501 Instructions for Use of G32R501 IDE and Tool</u> <u>Chain</u>" to enable pyOCD support for the G32R501 series chips.

# 6.2 Instructions for Dual-Core Debugging Using GEEHY-LINK (WinUSB)

This section provides a step-by-step guide for working with Eclipse and GEEHY-LINK (WinUSB) on the G32R5xx microcontroller.

In this example, a separate project needs to be created for each core.

(Example programs can be found at G32R5xx\_SDK\driverlib\g32r501\examples\eval\ipc)

- 1. Import the projects, and after ensuring successful compilation, configure the debug tabs as follows:

- Create a new debug configuration

- 1) Left-click the Debug icon to open the Debug configurations.

- 2) Select "Debug Configurations..." from the menu.

- 3) In the new window, right-click "GDB pyOCD Debugging."

- 4) Select "New Configuration" to create a new debug configuration.

|                                              |                                                          | -                                                                           |                                                           |                                      |                                         |        |     |     |    |       |

|----------------------------------------------|----------------------------------------------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------|--------------------------------------|-----------------------------------------|--------|-----|-----|----|-------|

| -                                            | *                                                        | 1) -                                                                        | ₽ -                                                       | <b>Q</b> -                           | i 🤌 😥                                   | s?     | · P |     | πŝ |       |

|                                              |                                                          | (no laur                                                                    | nch hist                                                  | tory)                                |                                         |        |     |     |    |       |

|                                              |                                                          | Debug                                                                       | As                                                        |                                      |                                         | >      |     |     |    |       |

|                                              |                                                          | Debug                                                                       | Config                                                    | uration                              | 5                                       |        | 2   |     |    |       |

|                                              |                                                          | Organiz                                                                     | ze Favo                                                   | rites                                |                                         |        |     |     |    |       |

| C GI<br>C GI<br>C GI<br>C GI<br>C GI<br>C GI | DB PyC<br>led_ex<br>DB QEI<br>DB QEI<br>DB QEI<br>DB QEI | enOCD [<br>DCD Deb<br>(1_blinky<br>MU aarc<br>MU arm<br>MU gnua<br>MU riscv | ougging<br>G32R5<br>h64 De<br>Debug<br>armeclip<br>32 Deb | 01 📑<br>bug pr<br>ging pose<br>ugg 👷 | New Co<br>New Pro<br>Export<br>Duplicat | ototyp |     | ] 4 |    | - Sel |

| 🗸 💽 GI                                       | DB SEG                                                   | MU riscv<br>GER J-L<br>nath_sar                                             | ink Deb                                                   | oug: 🗉                               | Link Pro<br>Unlink F                    | 1.1    |     |     |    |       |

|                                              |                                                          |                                                                             |                                                           |                                      |                                         |        |     |     |    |       |

#### Figure 27 New Configuration

- Configure the Main tab

- 1) Name the current debug configuration at the top.

- 2) Click "Browse..." to select the project corresponding to the current debug configuration.

- Select the corresponding debug elf file, for example: G32R501\ipc\_ex2\_mailbox\_polling\_cpu0.elf. The example uses a relative path to the project file but absolute paths are also supported.

#### Figure 28 Configure Main

| Name: ipc_ex2_mailbox_polling_cpu0 G32R501               |                                                          |

|----------------------------------------------------------|----------------------------------------------------------|

| 📄 Main 🕸 Debugger 🕨 Startup 🦃 Source 🔲 Common 🔀 SVD Path |                                                          |

| Project:                                                 |                                                          |

| ipc_ex2_mailbox_polling_cpu0                             | <u>B</u> rowse                                           |

| C/C++ Application:                                       |                                                          |

| G32R501\ipc_ex2_mailbox_polling_cpu0.elf                 |                                                          |

|                                                          | <u>V</u> ariables Searc <u>h</u> Project B <u>r</u> owse |

- Configure the Debugger tab

- 1) Disable the setting for launching the pyOCD GDB Server by Eclipse.

- 2) Set the GDB Client to connect to the appropriate core ports. The default ports are usually: core 0: 3333, core 1: 3334.

Figure 29 Dual-Core Simulation Debugger Tab

| ame: ipc_ex2_mailb | ox_polling_cpu0 G32R501                                                                                                         |  |  |  |  |  |  |  |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 🗋 Main 🕸 Debugg    | er 🕨 Startup 🤤 Source 🔲 Common 🔀 SVD Path                                                                                       |  |  |  |  |  |  |  |

| Start pyOCD loc    | ally 🚹                                                                                                                          |  |  |  |  |  |  |  |

| Executable path:   | C:\Users\apex800691\AppData\Local\Programs\Python313\Scripts\pyocd.exe                                                          |  |  |  |  |  |  |  |

| Actual executable: | C:\Users\apex800691\AppData\Loca\\Programs\Python\Python313\Scripts\pyocd.exe                                                   |  |  |  |  |  |  |  |

|                    | (to change it use the <u>global</u> or <u>workspace</u> preferences pages or the <u>project</u> properties page)                |  |  |  |  |  |  |  |

| GDB port:          | 3333 Allocate console for pyOCD                                                                                                 |  |  |  |  |  |  |  |

| Semihosting port:  | 4444 Selecter console for semihosting                                                                                           |  |  |  |  |  |  |  |

| Debug probe:       | <please a="" debug="" probe="" select=""></please>                                                                              |  |  |  |  |  |  |  |

| Default target:    |                                                                                                                                 |  |  |  |  |  |  |  |

| Override target    |                                                                                                                                 |  |  |  |  |  |  |  |

| Bus speed:         | ed: 1000000 V Hz                                                                                                                |  |  |  |  |  |  |  |

| Connect mode:      | t mode: Halt ~                                                                                                                  |  |  |  |  |  |  |  |

| Reset type:        | Default ~                                                                                                                       |  |  |  |  |  |  |  |

| Flash mode:        | Sector erase V Smart flash                                                                                                      |  |  |  |  |  |  |  |

| 🖂 Halt at hard fau | Halt at hard fault                                                                                                              |  |  |  |  |  |  |  |

|                    | nable semihosting                                                                                                               |  |  |  |  |  |  |  |

| Other options:     | her options:script E:\GIT\G32R501\g32r501_v0.6\driverlib\g32r501\examples\eval\led\led_ex1_blinky\project\Eclipse\pyocd_user.py |  |  |  |  |  |  |  |

|                    |                                                                                                                                 |  |  |  |  |  |  |  |

| GDB Client Setup   |                                                                                                                                 |  |  |  |  |  |  |  |

|                    | C:\GCC\10 2021.10\bin\arm-none-eabi-gdb.exe                                                                                     |  |  |  |  |  |  |  |

|                    |                                                                                                                                 |  |  |  |  |  |  |  |

|                    | C\GCC\10 2021.10\bin\arm-none-eabi-gdb.exe                                                                                      |  |  |  |  |  |  |  |

| Other options:     | target remote localhost:3333 2                                                                                                  |  |  |  |  |  |  |  |

| Commands:          | set mem inaccessible-by-default off                                                                                             |  |  |  |  |  |  |  |

|                    |                                                                                                                                 |  |  |  |  |  |  |  |

| Remote Target      |                                                                                                                                 |  |  |  |  |  |  |  |

| Host name or IP ad | dress: localhost                                                                                                                |  |  |  |  |  |  |  |

| Port number:       | 3333                                                                                                                            |  |  |  |  |  |  |  |

• Configure the Startup tab

cpu0: The CPU0 Startup tab follows the single-core configuration as detailed in the "AN1126\_G32R501 Instructions for Use of G32R501 IDE and Tool Chain".

cpu1:

1) In the commander tab, remove the decryption sequence, leaving only the PC setup commands. (Note that the start address of the cpu1 program must be modified. The example uses 0x08050000.)

```

set $t0 = *(unsigned int *)0x08050000

```

```

set $sp=$t0

```

```

set $t1 = *(unsigned int *)0x08050004

```

set \$pc=\$t1

```

set $xpsr=$xpsr|(1<<24)

```

2) Uncheck "Load executable".

Figure 30 Startup Tab

| Main 🏇 Debugger 🕨 Startup                                                                                                            | G32R501             | mmon 🖵 SVD Path       |     |               |             |

|--------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----------------------|-----|---------------|-------------|

| Initialization Commands                                                                                                              |                     |                       |     |               |             |

| <pre>set \$t0 = *(unsigned int *)0x08050 set \$sp=\$t0 set \$t1 = *(unsigned int *)0x08050 set \$t1 = *(unsigned int *)0x08050</pre> | 1                   |                       |     |               | ^           |

| Load Symbols and Executable<br>☑ Load symbols<br>◉ Use project binary: ipc ex2 m                                                     | nailbox polling cpu | 1.elf                 |     |               |             |

| O Use file:                                                                                                                          |                     |                       |     | <br>Workspace | File System |

| Symbols offset (hex): Coad executable O Use project binary: ipc_ex2_n                                                                | nailbox_polling_cpu | ı1.elf                |     |               |             |

| O Use file:                                                                                                                          |                     |                       |     | Workspace     | File System |

| Runtime Options<br>Debug in RAM                                                                                                      |                     |                       |     |               |             |

| Run/Restart Commands                                                                                                                 | Type: halt (alwa    | ays executed at Resta | rt) |               |             |

| <pre>set \$t0 = *(unsigned int *)0x08050 set \$sp=\$t0 set \$t1 = *(unsigned int *)0x08050 set \$sp=\$t1</pre>                       |                     |                       |     |               | ~           |

| Set program counter at (hex):<br>✓ Set breakpoint at:<br>✓ Continue                                                                  | main                |                       |     |               |             |

2. Start the pyOCD gdbserver from the terminal with the command:

### pyocd gdbserver

- The directory where pyOCD gdbserver is started should contain the following files:

- pyocd.yaml, the dual-core version, refer to SDK/device\_support/g32r501/common/pyOCD/

target\_override: g32r501dxx

frequency: 8000000 # Set 8 MHz SWD default for all probes

session:

enable\_multicore\_debug: true

persist: true

2) pyocd\_user.py, refer to SDK/device\_support/g32r501/common/pyOCD/

#### Figure 31 Terminal Start pyocd gdbserver

| 📾 C:\Windows\System32\cmd.exe - pyocd_gdbserver — 🗆 X                                                                                                                                                                                                                                                                                                   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| B:\GIT\G32R501\g32r501_v0.6\driverlib\g32r501\examples\eval\ipc\ipc_ex2_mailbox_polling>pyocd gdbserver<br>0001343 I Patched target_G32R501xx DECRYPT_KEYS via pyocd_user.py! [pyocd_user]<br>0001370 I Target type is g32r501dxx [board]<br>0001400 I DP IDR = 0x6ba02477 (v2 rev6) [dap]                                                              |

| 0001404 I AHB-AF#0 IDR = 0.824770001 (AHB-AF var0 rev8) [discovery]<br>0001405 I AHB-AF#1 IDR = 0.834770001 (AHB-AP var0 rev8) [discovery]<br>0001407 I AHB-AF#2 IDR = 0.834770001 (AHB-AP var0 rev8) [discovery]<br>0001409 I AHB-AF#0 Class 0x1 ROM table #0 @ 0xe00ff000 (designer=a75:Arm China part=4d2) [rom_table]<br>0001411 I [0]              |

| table]<br>0001413 I [1] <e0001000:dwt archid="1a02" china="" class="9" designer="a75:Arm" devid="0:0:0" devtype="00" part="d24" star-mc2=""> [rom_</e0001000:dwt>                                                                                                                                                                                       |

| table]<br>00014141 [2] <e0002000:bpu archid="1a03" china="" class="9" designer="a75:Arm" devid="0:0:0" devtype="00" part="d24" star-mc2=""> [rom<br/></e0002000:bpu>                                                                                                                                                                                    |

| table]<br>0001415 I [3] <e0000000:itm archid="1a01" china="" class="9" designer="a75:Arm" devid="0:0:0" devtype="43" part="d24" star-mc2=""> [rom<br/>table]</e0000000:itm>                                                                                                                                                                             |

| uane]<br>0001417 I [5] <e0041000:etm archid="4a13" china="" class="9" designer="a75:Arm" devid="0:0:0" devtype="13" part="d24" star-mc2=""> [rom<br/>table]</e0041000:etm>                                                                                                                                                                              |

| 0001418 I [6] <e0003000:??? archid="0a06" china="" class="9" designer="a75:Arm" devid="0:0:0" devtype="16" part="d24"> [rom_table]<br/>0001419 I [7]<e0042000:cti archid="la14" china="" class="9" designer="a75:Arm" devid="40800:0:0" devtype="14" part="d24" star-mc2=""> [<br/>rom table]</e0042000:cti></e0003000:???>                             |

| 0001420 T [8] <e0046000:pwc-100 archid="0a55" class="9" designer="43b:Arm" devid="145509d6:c105c04:0" devtype="55" part="9ba"> [ro<br/>m table]</e0046000:pwc-100>                                                                                                                                                                                      |

| 0001423 I AHB-AP#1 Class 0x1 ROM table #0 @ 0xe00ff000 (designer=a75:Arm China part=4d2) [rom_table]<br>0001425 I [0]<60006000:SCS Star=MC2 class=9 designer=a75:Arm China part=d24 devtype=00 archid=2a04 devid=0:0:0> [rom_<br>table]                                                                                                                 |

| 0001426 I [1] <e0001000:dwt archid="1a02" china="" class="9" designer="a75:Arm" devid="0:0:0" devtype="00" part="d24" star-mc2=""> [rom_<br/>table]</e0001000:dwt>                                                                                                                                                                                      |

| 0001428 I [2] <e0002000:bpu archid="la03" china="" class="9" designer="a75:Arm" devid="0:0:0" devtype="00" part="d24" star-mc2=""> [rom_<br/>table]</e0002000:bpu>                                                                                                                                                                                      |

| 0001430 I [3] <e0000000:itm archid="1a01" china="" class="9" designer="a75:Arm" devid="0:0:0" devtype="43" part="d24" star-mc2=""> [rom_<br/>table]</e0000000:itm>                                                                                                                                                                                      |

| 0001432 I [5] <e0041000:etm archid="4a13" china="" class="9" designer="a75:Arm" devid="0:0:0" devtype="13" part="d24" star-mc2=""> [rom_<br/>table]</e0041000:etm>                                                                                                                                                                                      |

| 0001433 I [6]<00003000:??? class=9 designer=a75:Arm China part=d24 devtype=16 archid=0a06 devid=0:0:0> [rom_table]<br>0001434 I [7]<0042000:CTI Star=MC2 class=9 designer=a75:Arm China part=d24 devtype=14 archid=1a14 devid=40800:0:0> [<br>rom_table]                                                                                                |

| 0001436 I [8] <e0046000:pmc-100 archid="0a55" class="9" designer="43b:Arm" devid="145509d6:c105c04:0" devtype="55" part="9ba"> [ro<br/>m table]</e0046000:pmc-100>                                                                                                                                                                                      |

| 0001439 I CPU core #0: Star-MC2 r0p1, v7.0-M architecture [cortex_m]<br>0001439 I Extensions: [DSP, FPU, FPU_DP, FPU_VS, MPU] [cortex_m]<br>0001439 I FPU present: FPV5-D16-M [cortex_m]                                                                                                                                                                |

| 0001440 I core0 is created and initialized. [target_G32R501xx]<br>0001440 I Enabling clock and setting startup address for core1 via APO [target_G32R501xx]<br>0001444 I CPU core HI: Star-WC2 ropl, v7.0-M architecture [cortex_m]<br>0001444 I Extensions: IDSP, FPU, FPU_DP, FPU_VS, MPU] [cortex_m]<br>0001444 I FPU present: FPV5-D16-M [cortex_m] |

| 0001445 I corel is created and initialized. [target_G32R501xx]<br>0001446 I 4 hardware watchpoints [dwt]                                                                                                                                                                                                                                                |

| 0001447 I 8 hardware breakpoints, 1 literal comparators [fpb]<br>0001450 I 4 hardware watchpoints [dwt]                                                                                                                                                                                                                                                 |

| 0001451 I 8 hardware breakpoints, 1 literal comparators [fpb]<br>r501 commect in did_commect                                                                                                                                                                                                                                                            |

| Reading SP/PC from 0x08000000;<br>MSP = 0x20003FF8<br>DFD = 0 concurrent                                                                                                                                                                                                                                                                                |

| PC = 0x08001F65<br>set pc_cmd: Resisters updated: target resuming.                                                                                                                                                                                                                                                                                      |

| 0001491 [ Semihost server started on port 4444 (core 0) [server]<br>0001869 [ GDB server started on port 3333 (core 0) [gdbserver]<br>0001872 [] Semihost server started on port 4445 (core 1) [server]                                                                                                                                                 |

| 0001872 I GDB server started on port 3334 (core 1) [gdbserver]                                                                                                                                                                                                                                                                                          |

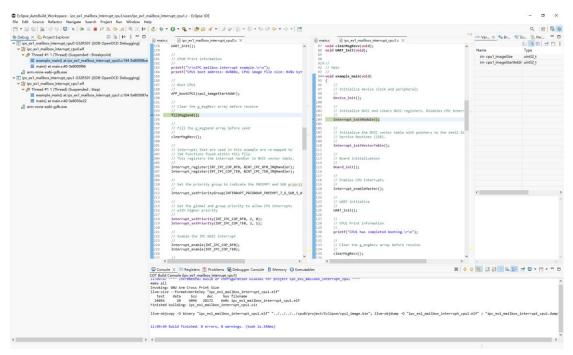

- 3. Start two debug sessions in Eclipse separately.

- Launch debugging for the CPU0 project and set a breakpoint after the statement that starts CPU1. In the example, set the breakpoint after the statement APP\_bootCPU1(cpu1\_imageStartAddr);

- Launch debugging for the CPU1 project.

- Perform dual-core debugging as needed.

- 1) Click the thread corresponding to cpu0 to control cpu0 simulation.

- 2) Click the thread corresponding to cpu1 to control cpu1 simulation.

Figure 32 Eclipse Simulation Debugging Interface

# 7 Revision

### Table 3 Document Revision History

| Date         | Version | Change History                                                 |

|--------------|---------|----------------------------------------------------------------|

| January 2025 | 1.0     | New                                                            |

| April 2025   | 1.1     | Add the new section about Eclipse dual-core debugging support. |

## Statement

This document is formulated and published by Geehy Semiconductor Co., Ltd. (hereinafter referred to as "Geehy"). The contents in this document are protected by laws and regulations of trademark, copyright and software copyright. Geehy reserves the right to make corrections and modifications to this document at any time. Read this document carefully before using Geehy products. Once you use the Geehy product, it means that you (hereinafter referred to as the "users") have known and accepted all the contents of this document. Users shall use the Geehy product in accordance with relevant laws and regulations and the requirements of this document.

#### 1. Ownership

This document can only be used in connection with the corresponding chip products or software products provided by Geehy. Without the prior permission of Geehy, no unit or individual may copy, transcribe, modify, edit or disseminate all or part of the contents of this document for any reason or in any form.

The "极海" or "Geehy" words or graphics with "®" or "<sup>™</sup>" in this document are trademarks of Geehy. Other product or service names displayed on Geehy products are the property of their respective owners.

#### 2. No Intellectual Property License

Geehy owns all rights, ownership and intellectual property rights involved in this document.

Geehy shall not be deemed to grant the license or right of any intellectual property to users explicitly or implicitly due to the sale or distribution of Geehy products or this document.

If any third party's products, services or intellectual property are involved in this document, it shall not be deemed that Geehy authorizes users to use the aforesaid third party's products, services or intellectual property. Any information regarding the application of the product, Geehy hereby disclaims any and all warranties and liabilities of any kind, including without limitation warranties of non-infringement of intellectual property rights of any third party, unless otherwise agreed in sales order or sales contract.

#### 3. Version Update

Users can obtain the latest document of the corresponding models when ordering Geehy products.

If the contents in this document are inconsistent with Geehy products, the agreement in the sales order or the sales contract shall prevail.

#### 4. Information Reliability

The relevant data in this document are obtained from batch test by Geehy Laboratory or cooperative third-party testing organization. However, clerical errors in correction or errors caused by differences in testing environment may occur inevitably. Therefore, users should understand that Geehy does not bear any responsibility for such errors that may occur in this document. The relevant data in this document are only used to guide users as performance parameter reference and do not constitute Geehy's guarantee for any product performance.

Users shall select appropriate Geehy products according to their own needs, and effectively verify and test the applicability of Geehy products to confirm that Geehy products meet their own needs, corresponding standards, safety or other reliability requirements. If losses are caused to users due to user's failure to fully verify and test Geehy products, Geehy will not bear any responsibility.

#### 5. Legality

USERS SHALL ABIDE BY ALL APPLICABLE LOCAL LAWS AND REGULATIONS WHEN USING THIS DOCUMENT AND THE MATCHING GEEHY PRODUCTS. USERS SHALL UNDERSTAND THAT THE PRODUCTS MAY BE RESTRICTED BY THE EXPORT, RE-EXPORT OR OTHER LAWS OF THE COUNTRIES OF THE PRODUCTS SUPPLIERS, GEEHY, GEEHY DISTRIBUTORS AND USERS. USERS (ON BEHALF OR ITSELF, SUBSIDIARIES AND AFFILIATED ENTERPRISES) SHALL AGREE AND PROMISE TO ABIDE BY ALL APPLICABLE LAWS AND REGULATIONS ON THE EXPORT AND RE-EXPORT OF GEEHY PRODUCTS AND/OR TECHNOLOGIES AND DIRECT PRODUCTS.

#### 6. Disclaimer of Warranty

THIS DOCUMENT IS PROVIDED BY GEEHY "AS IS" AND THERE IS NO WARRANTY OF ANY KIND, EITHER EXPRESSED OR IMPLIED, INCLUDING, BUT NOT LIMITED TO, THE WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE, TO THE EXTENT PERMITTED BY APPLICABLE LAW.

GEEHY'S PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED FOR USE AS CRITICAL COMPONENTS IN MILITARY, LIFE-SUPPORT, POLLUTION CONTROL, OR HAZARDOUS SUBSTANCES MANAGEMENT SYSTEMS, NOR WHERE FAILURE COULD RESULT IN INJURY, DEATH, PROPERTY OR ENVIRONMENTAL DAMAGE.

IF THE PRODUCT IS NOT LABELED AS "AUTOMOTIVE GRADE," IT SHOULD NOT BE CONSIDERED SUITABLE FOR AUTOMOTIVE APPLICATIONS. GEEHY ASSUMES NO LIABILITY FOR THE USE BEYOND ITS SPECIFICATIONS OR GUIDELINES.

THE USER SHOULD ENSURE THAT THE APPLICATION OF THE PRODUCTS COMPLIES WITH ALL RELEVANT STANDARDS, INCLUDING BUT NOT LIMITED TO SAFETY, INFORMATION SECURITY, AND ENVIRONMENTAL REQUIREMENTS. THE USER ASSUMES FULL RESPONSIBILITY FOR THE SELECTION AND USE OF GEEHY PRODUCTS. GEEHY WILL BEAR NO RESPONSIBILITY FOR ANY DISPUTES ARISING FROM THE SUBSEQUENT DESIGN OR USE BY USERS.

#### 7. Limitation of Liability

IN NO EVENT, UNLESS REQUIRED BY APPLICABLE LAW OR AGREED TO IN WRITING WILL GEEHY OR ANY OTHER PARTY WHO PROVIDES THE DOCUMENT AND PRODUCTS "AS IS", BE LIABLE FOR DAMAGES, INCLUDING ANY GENERAL, SPECIAL, DIRECT, INCIDENTAL OR CONSEQUENTIAL DAMAGES ARISING OUT OF THE USE OR INABILITY TO USE THE DOCUMENT AND PRODUCTS (INCLUDING BUT NOT LIMITED TO LOSSES OF DATA OR DATA BEING RENDERED INACCURATE OR LOSSES SUSTAINED BY USERS OR THIRD PARTIES). THIS COVERS POTENTIAL DAMAGES TO PERSONAL SAFETY, PROPERTY, OR THE ENVIRONMENT, FOR WHICH GEEHY WILL NOT BE RESPONSIBLE.

#### 8. Scope of Application

The information in this document replaces the information provided in all previous versions of the document.

© 2025 Geehy Semiconductor Co., Ltd. - All Rights Reserved

# Geehy Semiconductor Co.,Ltd.